エレクトロニック・デザイン・オートメーション(EDA)の技術革新の中で、UVM(Universal Verification Methodology)以上のインパクトを与えたものはないでしょう。何十年もの間、設計者中心の場当たり的なシミュレーションや、より自動化された手法を用いた少数の先進的な検証チームは存在していましたが、UVMはチップ開発に携わるすべての人々に新しい時代をもたらしました。検証エンジニアは、オブジェクト指向プログラミング、制約付きランダム・スティミュラス、セルフチェック・テスト、再利用可能なモデル、機能カバレッジ、アサーションなどをすぐに利用できるようになりました。UVM自体とそれを基にしたSystemVerilog言語はどちらも業界標準であり、チームは複数のベンダのEDAツールを組み合わせたり、必要に応じてツールを簡単に切り替えたりすることができます。

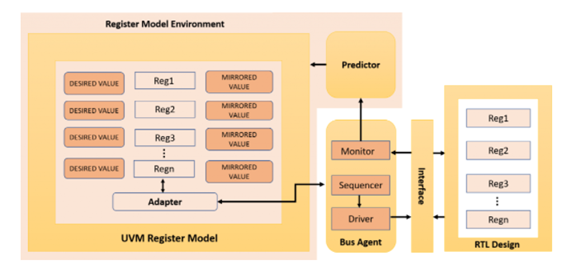

この記事では、UVM Register Abstraction Layer (RAL)に焦点を当てます。昨今の大規模なシステムオンチップ(SoC)設計には、多くの制御レジスタやステータス・レジスタが含まれており、多くの場合、ハードウェアだけでなく、組み込みソフトウェアやドライバからもアクセスできます。これらのレジスタが正しく動作するかどうかを確認することは、検証の初期段階として重要であり、その後、デザインの残りの部分の機能テストを実行しながら、レジスタを操作し、追跡する必要があります。UVM RALは、標準化されたベースクラス・ライブラリとメソッドのセットを提供しており、デザイン内のメモリ・マップド・レジスタとメモリにアクセスするためのオブジェクト指向モデルを容易に構築することができます。このモデルには、デザイン内のレジスタの値をミラーリングするレジスタ・コンポーネントが含まれており、テスト結果をチェックするためにレジスタの期待値を保持します。

検証エンジニアは、以下のメソッドを含むアプリケーション・プログラミング・インターフェース(API)を利用することができます。

write()/read()

RTL(レジスタ・トランスファー・レベル)デザイン上で物理的な書き込み/読み取りを実行する。書き込みの後、ミラーリングされた値が更新される。

poke()/peek()

物理インタフェースをバイパスして,RTLレジスタに直接書き込み/読み取りを行う。書き込みの後、ミラーリングされた値が更新される。

セット()/ゲット()

デザインにアクセスすることなく、目的の値のコンポーネントを直接書き込む/読み取る。

update()

目的の値がミラーリングされた値と異なる場合は、write()メソッドを呼び出します。

したがって、ミラーリングされた値が更新される。

ミラーリング()

read()メソッドを呼び出し、ミラーリングされた値をRTLデザインと一致するように更新する。更新前に設計値とミラーリングされた値を比較してもよい。

UVM RALには、今日のSoCの複雑なレジスタやメモリ構造を反映したモデルを作成するための多くの機能が用意されています。各レジスタには複数のフィールドがあり、それぞれが独立して読み書きできます。複数のレジスタはレジスタ・ファイルにまとめられ、レジスタ・ファイルには任意の数のレジスタやサブファイルを含むことができます。レジスタ・ブロックは,任意の数のレジスタ,レジスタ・ファイル,メモリ,またはサブブロックを含むことができる。レジスタモデルの各要素(フィールド、レジスタ、レジスタ・ファイル、メモリ、ブロック)には、その要素に対する読み取りと書き込みの操作を抽象化したクラス・インスタンスがあります。UVM RALは、ハードウェア物理インタフェースを使用したフロントドア・レジスタ・アクセスと、RTLレジスタに直接アクセスするバックドア・アクセスの両方をサポートしています。また、UVM RALには、レジスタやメモリの検証に使用できる定義済みのテストケースを含むレジスタテストシーケンス・ライブラリが含まれています。

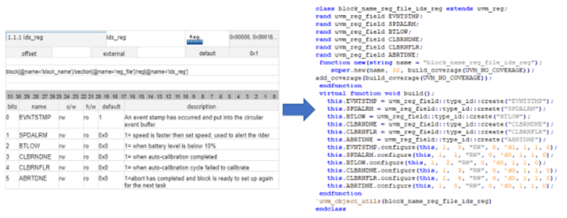

このような柔軟性とパワーを持つUVM RALのモデルを書くことは、些細な作業ではありません。標準的な基本クラス、メソッド、シーケンスは素晴らしい基盤となりますが、検証チームはRALモデルの作成をできるだけ自動化したいと考えています。幸いなことに、これらのモデルとRTLコードを同時に、共通の仕様から自動生成することは容易です。Agnisys社のIDesignSpec(IDS)ソリューションはこの機能を提供し、SystemRDL規格を含む多くの仕様フォーマットをサポートしています。さらに自動化を進めるために、検証エンジニアは、Agnisysが提供するMicrosoft WordやMicrosoft Excelのプラグインを使用して、直感的なグラフィック形式でレジスタを指定することができます。下の図では、6つのビットフィールドを持つレジスタを指定しています。IDSはこの入力を受けて、矢印の右に示すUVM RALモデルを自動的に生成します。

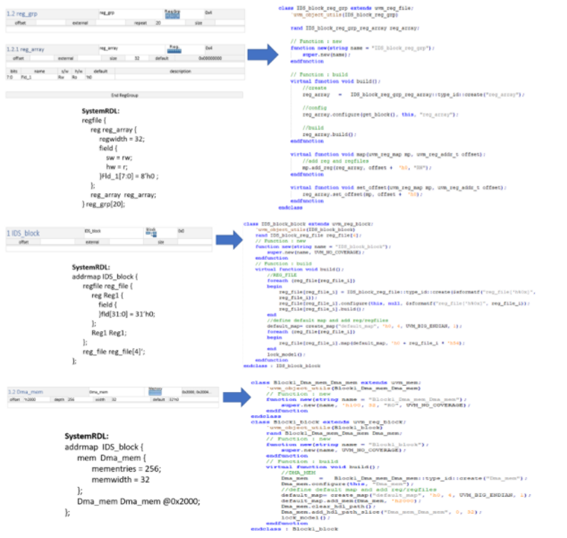

次の図に示すように、レジスタ・ファイルの指定も同様に簡単です。対応するSystemRDLの記述が含まれています。SystemRDL は IDS から出力される可能性のあるものの一つですが、Agnisys IDS-NG ソリューションに含まれるプラグインや専用エディタを使わずに手動で記述したいユーザーにとっては、入力にもなります。また、複数のレジスタ・ファイルを含むレジスタ・ブロックや、メモリの定義についても説明しています。

IDSには、SoCデザインの多様性を反映するための多くのオプションが用意されています。レジスタ、フィールド、ビットは、読み取り/書き込みまたは読み取り専用として指定でき、ハードウェアとソフトウェアのアクセスで異なる値を設定できます。これは、ブート時に組み込みソフトウェアによって設定され、その後読み込まれるが、ハードウェア・デザインによって変更されることのないコンフィギュレーション・レジスタに特に有効です。IDSは、シャドウ、ロック、トリガバッファ、割り込み、カウンタ、外部など、20種類以上の特殊レジスタをサポートしています。生成されたRTLデザインとUVM RALモデルは、これらのオプションを正確に反映しています。IDSはオプションで、生成されたレジスタモデルに機能カバレッジを含めることができます。これには、読み書きされるビットのカバレッジ、フィールドの値のカバレッジ、アドレスマップで読み書きされるアドレスのカバレッジ、またはこれらの組み合わせのカバレッジが含まれます。ユーザーは、特定のレジスタやブロックに対してどのようなタイプのカバレッジ・コードを生成するかを完全にコントロールすることができます。

RALは、UVMが実現する高度な検証技術の良い例です。SoC開発チームは、任意の複雑なレジスタやメモリを定義することができ、これらの構造を含む設計の検証を安心して行うことができます。Agnisys IDSは、RTLコード、UVM RALモデル、組み込みプログラマ用のC/C++ヘッダー、複数のドキュメントを簡単に指定・自動生成することで、レジスタやメモリの設計・検証を次のレベルに引き上げます。この機能は、SoCチームのすべてのメンバー、特にUVMベースのテストを作成・実行する検証エンジニアにとって有益です。