IC スペック オートメーション

IC Designer Guide to Automate Spec of Design Verification & Validation (agnisys.com)

~自動化ソリューションでIC設計を改善し、エラーを削減る課題と方法~

100%設計ミスが存在しないICチップの開発販売は困難で、長年の課題です。

設計チームは、より効率的で強力なICの需要に応えることが期待されていますが、これらの多様で複数のチームに所属する設計者へ、個人スキルに依存した期待が拡大する一方で、“超人”ではありません。そのため、“まれに“RTL(Register-Transfer-Level)設計のコーディングでミスが発生したり、検証で見落としが発生したりすることがあります。エラーを完全になくすというのは高い目標かもしれませんが、Agnisysではあくなき情熱をもってそれを追求しています。

カリフォルニア大学バークレー校のアルベルト・サンジョバンニ・ヴィンセンテリ教授は、「BBVA Foundation Frontiers of Knowledge Award in Information and Communication Technologies」を受賞し、現代の半導体産業が抱える深刻な問題に対処するための新しいツール、技術、方法論を開発する電子設計自動化(EDA)産業の誕生につながった優れた貢献が評価されました。

昨今も、EDA企業は、エラーの数と深刻さを減らすために最善を尽くしています。Agnisysでは、チップを交換しなければ修正できないショーストッパー的なバグと、パフォーマンスへの影響を最小限に抑えたソフトウェアの回避策で解決できるマイナーな問題との間に大きな違いがあることを認識しています。

EDAに携わる私たちは、お客様がより複雑なチップやIP(知的財産)を提供することに集中できるよう、お客様の負担を軽減し、課題に対処できるよう日々努力しています。

~仕様の解釈の齟齬やスペックの変更に関する悩み~

Agnisysでは、お客様の悩みを理解するために、仕様の自動化に重点を置いてきました。その結果、お客様から「業界で最も広範なソリューションを持っている」とよく言われます。

私たちがこの特別な焦点を選んだのにはいくつかの理由があります。ICチップのバグは、仕様の誤りや、仕様の解釈の相違が大きな原因であることが判明しています。これは、正式な調査だけでなく、逸話的な証拠によっても、長年にわたって実証されてきました。過去数年間の特に注目すべきニュースを列挙すると、「Tiny Chips, Big Errors」、「Tiny Chips Cause Giant Error Correction Challenges」、「参考:今日のコンピュータチップは非常に高度で、正確というより「メルヘン」であり、これがその証拠だ」など、IC仕様に関するトラブルについては、私たちが真実だとわかっていることをさらに裏付けるものであり、今日のますます複雑になるチップ納入に重大な障害となっています。

ウィルソン・リサーチ・グループの機能検証研究は、シーメンスEDA(旧メンター・グラフィックス)が2年ごとに主催しているもので、その重要な参考資料の1つです。シーメンスEDAのデザイン検証技術部門のチーフサイエンティストであり、検証アカデミーの共同設立者兼エグゼクティブエディターであるハリー・フォスターは、その結果をうまくまとめており、2022年の研究からの統計は我々の議論に大いに関連するものです:

・フィールドプログラマブルゲートアレイ(FPGA)の機能的欠陥の55%以上は、仕様の誤りや不完全さが根本原因である。

・FPGAの機能欠陥の50%以上は仕様変更が根本原因

・特定用途向け集積回路(ASIC)の機能欠陥の45%以上は、仕様の誤りや不完全さが根本的な原因となっている

・ASICの機能欠陥の40%以上は仕様変更が根本原因

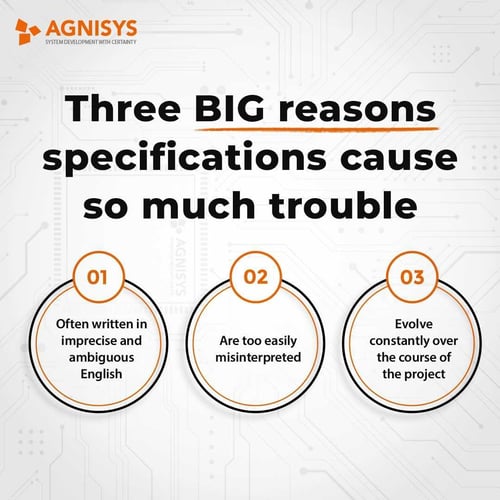

仕様書が問題を引き起こすのには、3つの大きな理由があります。

1つ目は、、ほとんどの仕様書は英語のような自然言語で書かれており、本来は不正確で曖昧なものであり、エンジニアが読んでも正しく解釈できないことがあります。

この問題は、複数のチームが同じ仕様書を読み、解釈することでさらに深刻化します。

RTL設計者、検証エンジニア、組み込みプログラマー、ラボの立ち上げチーム、テクニカルライター、その他が関与しています。

2つ目に、それぞれのチームは、仕様の解釈が異なる可能性があります。仕様が不正確である以上、当然といえば当然です。これは、2人の設計者が共有インターフェイスを矛盾なく実装する場合のように、設計上のエラーに直接つながります。また、検証チームがコーディングしたテストベンチがRTLハードウェアと整合しない場合など、不必要なデバッグ作業が発生し、プロジェクトのスケジュールを遅らせることになります。プログラマーと設計者の解釈の違いが、顧客の現場での使用に至るまで問題を引き起こすことは、先に挙げたニュースでも取り上げられたとおりです。

3つ目の大きな問題は、ICの仕様がプロジェクト期間中に常に変化していることです。たとえどのチームも同じように解釈していたとしても、仕様が更新されるたびに、ハードウェア設計、検証コード、組み込みプログラム、ドキュメントの変更に波及してしまい、残念なことに、このような繰り返しは貴重なプロジェクトリソースを消費し、解釈の相違や結果としてのバグが発生する新たな機会につながる可能性があります。

~業界をリードする仕様自動化の実現~

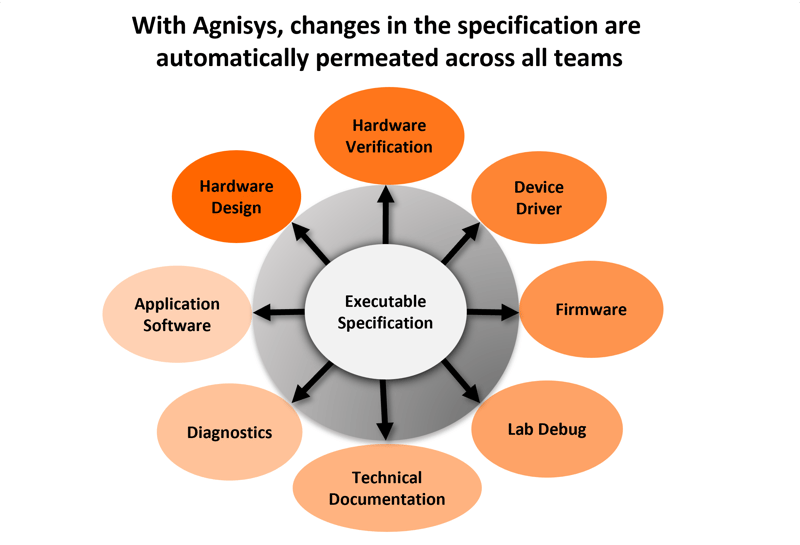

Agnisysは、仕様に焦点を当ています。IC仕様の不正確さ、解釈の違い、手作業による繰り返しを排除するために、IDesignSpec Suiteを開発したのです。仕様の自動化におけるEDA業界のリーダーとして、当社は、実行可能で曖昧さのないフォーマットでIC設計を指定し、現在市場で入手可能な最も多くのチップ関連ファイルを自動的に生成することを可能にします。当社のソリューションは、仕様書から直接RTLコードを生成し、構築上正しいIC設計を実現します。

IC Designer Guide to Automate Spec of Design Verification & Validation (agnisys.com)

さらにAgnisysは、検証に使用されるモデルやテストシーケンス、検証のための環境、生産プログラム内で使用される組み込みコードも生成します。実際、テクニカルライターがユーザーマニュアルに掲載できるほどの高品質なドキュメントを生成することができ、これらのファイルはすべて同じ仕様から生成されるため、常に一貫性が保たれています。これにより、曖昧なテキスト文書を手作業で解釈することに起因するバグを排除することができます。

そして何より、このような利点はプロジェクトで何度でも再利用可能です。仕様が変わるたびに、ボタンを押すだけで、すべての出力ファイル(合成可能なRTL、UVM RAL、Cヘッダー、ドキュメントなど)が自動的に再生成され、変更を反映するために必要に応じて更新されます。手作業は一切なく、各チームが使用するファイルは同期され、一貫性を保ちます。このように、Wilsonの調査で報告された機能的欠陥の2大原因に直接取り組み、解消することができるのです。

レジスタ、メモリ、プログラミングシーケンス、ステートマシン、データパス、ブロック間接続など、今日、ICの多くを実行可能なフォーマットで指定することができます。また、お客様の声に耳を傾け、ニーズを先取りして開発しているため、常に新しい機能を追加し、新しい設計スタイルをサポートしています。仕様書さえあれば、先に述べたすべてのファイルを自動生成し、仕様を変更するたびに即座に更新することができます。

~ファーストシリコンの成功に向けて走り出す~

わたしたちは、チップ設計チームと同じように、常に奇跡を起こすことができない“人間”です。そのため、システムオンチップ(SoC)全体の仕様書を作成することはできませんが、そこからすべてのハードウェアとソフトウェアを生成します。しかし、私たちは、ソリューションの範囲を広げるために、常に革新的な取り組みを行っています。特に活発なのは、人工知能(AI)や機械学習(ML)を使って、自然言語を含むより幅広いフォーマットの仕様書から、より多くの情報を推測することです。この分野に興味がある方は、ぜひ ispec.ai.をご覧ください。

このブログでは、私たちの進化をお伝えし、実体験を共有してくださる実際のお客様からの事例をご報告していきますので、必ずご覧ください。私たちは、バグが全くないチップをリリースする方法を知ることはできないかもしれませんが、バグの主な根本原因を取り除く方法を知っています。しかし、私の言葉を鵜呑みにしないでください。Agnisysとの協業がいかにお客様の設計を改善し、エラーを減らすことができるか、デモのご依頼や弊社チームメンバーとの打ち合わせは下記よりお問い合わせください。

ネクストリームお問い合わせ:inquiry@nextream.bz

設計エラーの原因は複数ありますが、最も一般的なものは、設計仕様と、それが製品開発のライフサイクルを通じてどのように配布され維持されているかに関連しています。この問題に対処する方法については、『The IC Designer’s Guide to Automated Specification of Design and Verification, for Better Products. 』をお読みください。