フレキシブルなリント,CDC解析で検証時間を短縮

ビジュアル化されたリント、CDC解析環境を活用することで、

発見されたエラーやワーニングの個所をブロックダイアグラム上で確認でき、

ブロック・ダイアグラムから直接ソースコードを表示し、その場で修正可能です。

日本のユーザ向けにSTARCルールを完備しており、

FPGAではAMD UltraFastルール、Latticeにも対応しています。

またスマート・エディタを使用することで、

コーディングしながらリアルタイムに構文チェックを行うことができます。

複雑化するFPGAでは今後リントやCDCが重要になると言われています。

この機会に使いやすいBluePearlの環境をご確認下さい。

Blue Pearl Visual Verification Suiteは、リント、CDCツールを提供しており、クロックの完全性とともに、回路とSDCの品質を保証することで、EDAおよびFPGAベンダーが提供するRTLシミュレーション・ベースの検証を補完します。

特別な専門家しか使えない他社製品と異なり、 Visual Verification Suiteは3時間程度のトレーニングで使えるだけでなく、

短時間でエラーの発見と修正が可能な、統合された低コストで使いやすい、リントおよびクロック・ドメイン・クロッシングの解析およびグラフィカルなデバッグ環境を提供しています。

Blue PearlのHP:http://www.bluepearlsoftware.com/

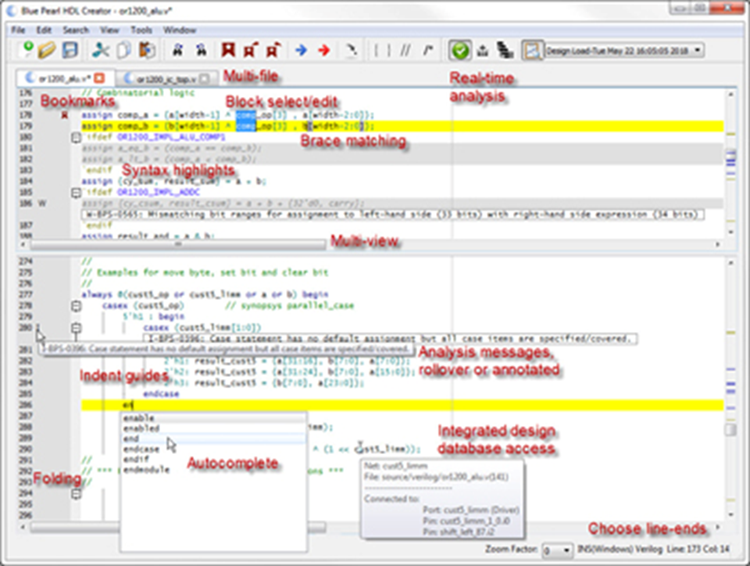

高品質なRTLとテストベンチを短期間で開発するためのスマート・エディタ:HDL Creator

HDL Creator は、高品質なRTLとテストベンチを短期間で開発するためのスマート・エディタです。 HDL Creatorは、シンタックスおよびコード・スタイルをリアルタイムにチェック可能な、直感的で使い易いエディタです。

コーティング中に2,000を超える文法チェック、100以上の構造解析をリアルタイムに実行することで、コード上の問題を直ちに修正可能です。

さらに、HDL Creator は、高度なデザイン・ビューを提供しており、コード構成の理解と修正を効率良く行えます。また現在お使いのエディタと一緒に使用することも可能になっています。

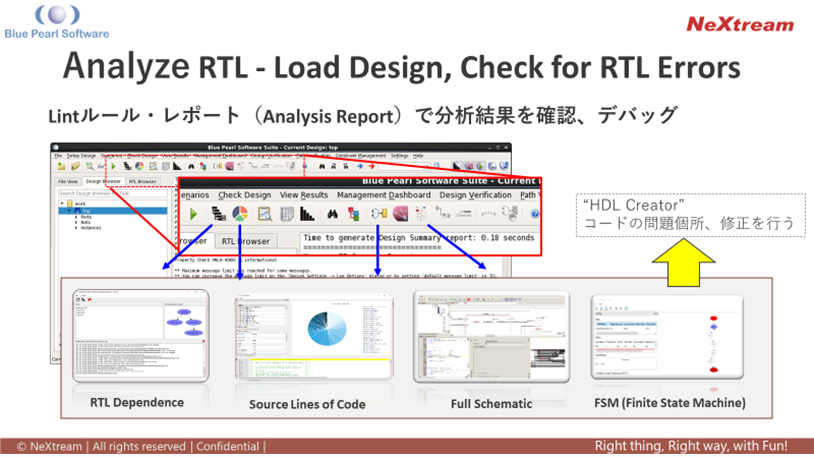

リントとデバッグの統合環境:Analyze RTL

RTLを広範囲に静的解析し、リンティングとデバッグを行うことで、エラーの無い高いQoRと高品質なRTLを実現します。Analyze-RTLでは、業界標準ルールおよびユーザ固有の設計ルールを定義できるだけでなく、

高機能なソート、メッセージのフィルタ能力を駆使し、ブロック・レベルからトップ・レベルのウェイバ集約機能等を活用することで、デザインの問題点を素早く見つけて、直ちに修正できます。

特長

- IEEE Verilog/SystemVerilog およびVHDL の言語仕様準拠

- DO‐254, STARC, and Xilinx® UltraFastなどの標準チェックをサポート

- RTL、回路図、メッセージ・ビュアの統合環境を用いた効率的なデバッグ

- メッセージを素早くソート、フィルタリングする機能と、ウェービングによる問題の特定

- コマンド・ライン・インターフェース (CLI)による自動化と、再利用可能なウェイバー・ファイル

- セットアップ・ウィザードを利用することで、短時間で利用可能

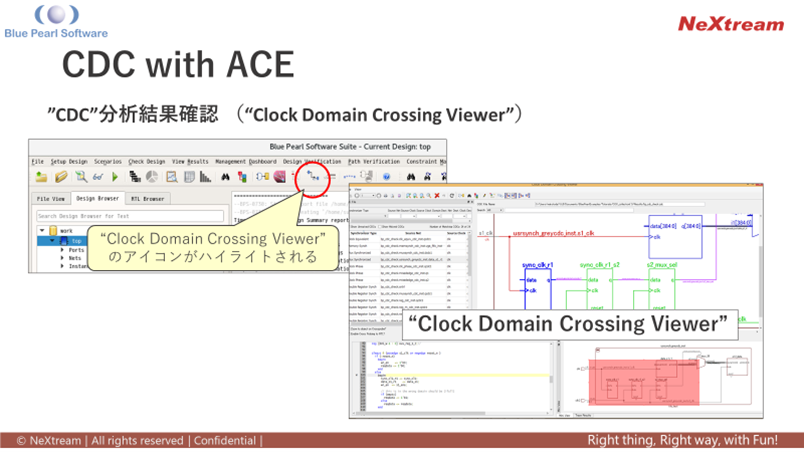

先進のCDC(クロック・ドメイン・クロッシング)解析環境:CDC Analysis

CDC解析を用いることで、同期における問題が無いことを保証します。

クロックとクロック・ドメインの相互作用、および同期と非同期の視覚化に加えて、暗号化されたIPをユーザ・グレーセルとしてモデル化することで、暗号化されたIPのCDCも確実に考慮します。

特長

- GUIまたはバッチ・モードによるCDC解析

- さまざまなシナリオを用いた容易なCDC解析

- 特定グループ解析による簡易なセットアップ

- TCLパーサを用いて、既存のクロック・ドメインが定義されたファイルを入力

- 相互作用しているクロック間の、同期に関する問題を特定

- クロック・ドメイン・クロッシング解析の種類:

・ Missing synchronizers

・ Re-converging paths

・ Combinational logic in synchronizers

・ Combinational logic before synchronizer

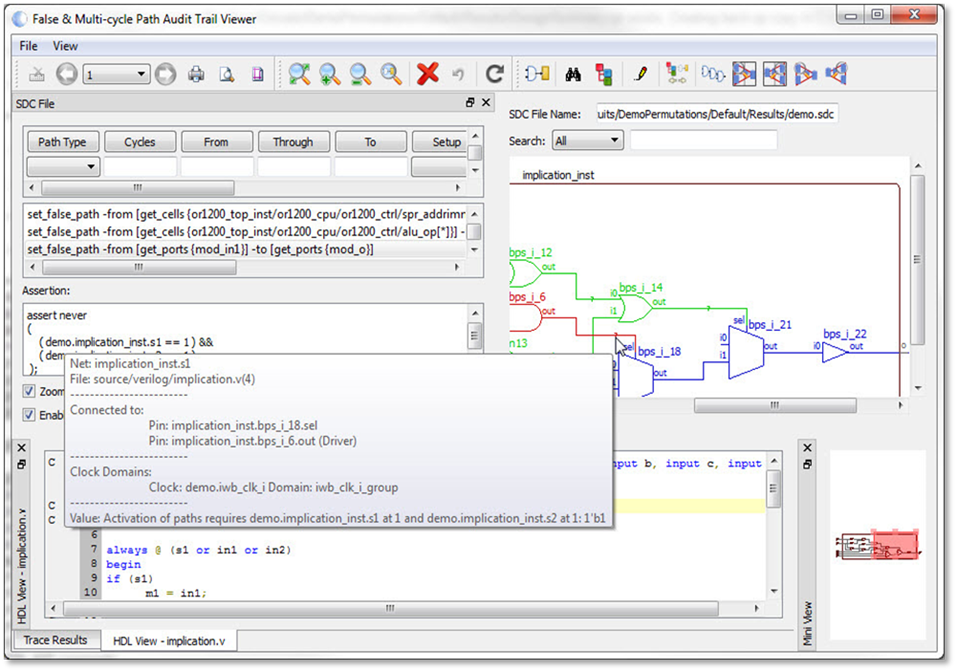

SDC自動生成機能:Automatic SDC Generation

RTL内のフォルス・パスとマルチサイクル・パスを識別し、下流の実装ツールへの制約とします。さらに、RTLシミュレーション・ツールの入力となるSVAまたはPSLを自動生成します。

特長

- FSMと制御動作の解析

- フォルス・パスとマルチサイクル・パスのシーケンシャル解析

- 例外タイミング制約の生成

・ Capitalize signals in signals crossing clock domains

・ Resets and constrained signals

・ Configuration registers

・ Functional false paths (FPs)

・ Multicycle paths (MCPs)

・ Block level MCPs where cyclic signals emanate from block ports

- 異なるSDCファイルの制約を比較

- ブロック・レベルにおける制約を、トップ・レベル制約に移行

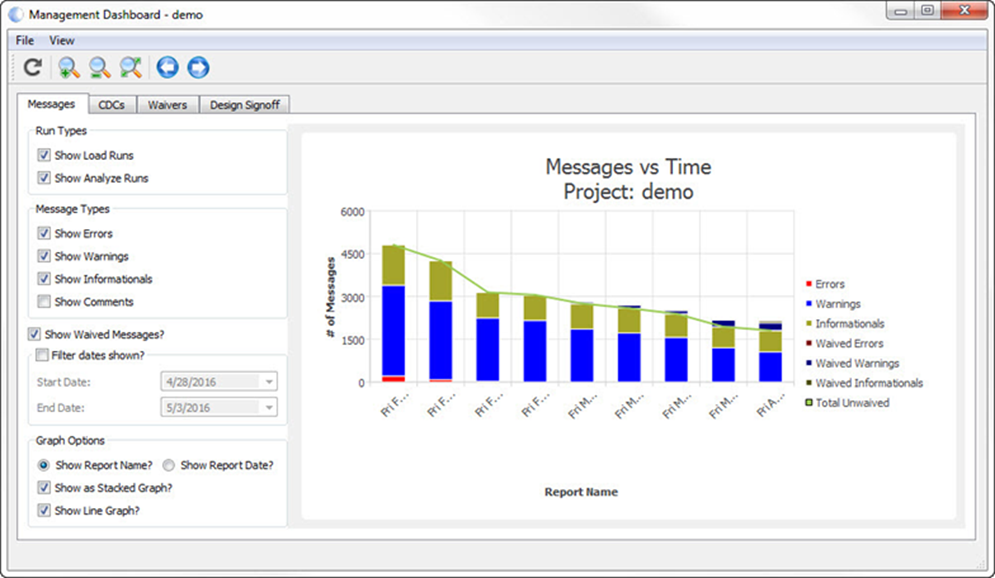

RTL検証結果をリアルタイムに可視化:Management Dashboard

RTL検証結果をリアルタイムに可視化します。ドキュメントやデザイン・レビューに合わせてカスタマイズ可能なプロジェクトレポートを提供します。

レポートは、Analyze RTLとCDC Analysis の両方について、カバレッジ、エラー、ワーニング及びウェイバの状況を確認可能です。 デザイン・サインオフ機能によって、デザインに対して、予め決められている必須のルールチェックがおこなわれ、全てパスしていることを確認できます。