仕様の自動化における課題として、以下のような項目が挙げられます。

・膨大で複雑なコントロールレジスタとステータスレジスタのセットの設計

・クロック・ドメイン・クロッシングの適切な処理

・標準規格に準拠したブロックのための堅牢かつ柔軟なIPの取得

・複雑なバスプロトコルのサポート

・IPとカスタムブロックの相互接続

・機能安全やセキュリティの要求を満たすことができる

IDS-NG™を用いることで、実行可能な仕様を作成しその仕様データから各種ファイルを自動生成することで、設計者が書かなければならないRTL(レジスタ・トランスファー・レベル)コードの量を大幅に削減できます。Agnisysのレジスタの自動化はおそらく最もよく知られた機能であり、Agnisysはこの分野で長年にわたり業界をリードしてきました。

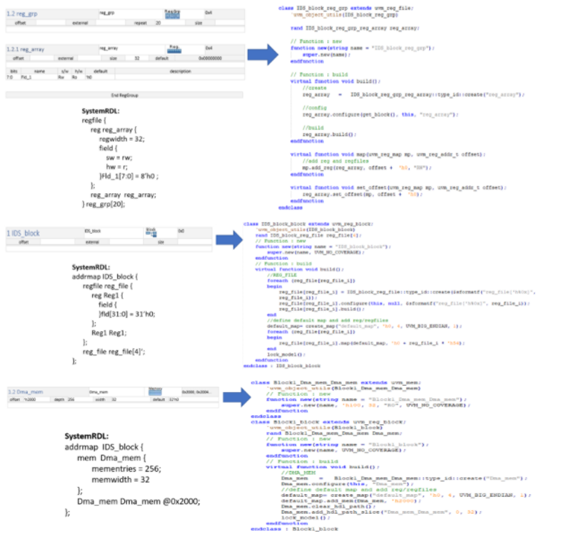

IDS-NGでは直感的な仕様エディタで、レジスタ、レジスタフィールド、レジスタファイル、レジスタグループ、メモリを指定することができます。また、SystemRDL規格を含む幅広い一般的なフォーマットの既存の仕様書をインポートし、必要に応じてエディタで修正することもできます。

指定されたレジスタの完全なRTLデザインが自動生成されるので、設計チームは関連するコーディング作業から解放されます。また、検証エンジニア向けにはUVM(Universal Verification Methodology)モデルを、組み込みプログラマ向けにはC/C++ヘッダーを、テクニカルライター向けにはドキュメントが自動生成されます。これにより、仕様の解釈の違いや、設計チーム間で異なるバージョンの仕様を参照するといったミスに起因するバグを排除することができます。仕様変更のたびに、すべてのチームがIDS-NGを用いて各種ファイルを自動生成することで、全てのチームにおける同期が保たれます。

また、クロックドメインクロッシング(CDC)におけるメタスタビリティなどの問題を回避するために必要なRTLコードの生成も行います。レジスタを作成する際に、システムバスとは異なるクロック・ドメインにある場合や、システムバスや他のハードウェア・デザインと異なる独自のクロック・ドメインにあることをツールが自動で検出します。また、2レベル・フリップフロップ、マルチプレクサ、ハンドシェイクなど、CDCバウンダリ間の同期をサポートしています。更にCDCのフォーマル解析に必要なアサーションを生成することで、検証チームを支援します。

IPジェネレーターのSLIP-G™の紹介

設計者はカスタマイズ可能な多くのオプションを持つSLIP-Gを使用し、GPIO(General Purpose Input/Output)、I2C、タイマー、PIC(Programmable Interrupt Controller)、DMA(Direct Memory Access)、SPI(Serial Peripheral Interface)、PWM(Pulse Width Modulation)、AES(Advanced Encryption Standard)などのデザインIPを手元で設計することが可能です。いずれのIPも、RTLのデザインだけでなく、UVMモデル、プログラミング・シーケンス、ドキュメントが自動生成されます。

典型的なSoCには、標準ベースのIP、IPベンダからライセンスされたデザイン、自社開発のデザインなど、何千ものブロックがあります。これらすべてのブロックをトップレベルのチップに組み立てるのは、大掛かりでかなり面倒な作業です。幸いなことに、IDS-NGはこのプロセスも自動化してくれます。当然のことながら、IDS-NGはSLIP-Gによって生成されたデザイン・ブロックを相互接続するために必要なRTLコードを全て生成します。また、カスタムブロックをどのように統合するかを指定することもでき、その部分のRTLコードも生成します。最後に、必要に応じて標準バス用のRTLアグリゲータ、ブリッジ、マルチプレクサも生成可能です。