Agnisys の主力ツールである IDesignSpec には、IDesignSpec GDI (グラフィカル版)と IDS-Batch CLI(コマンド版) の 2 種類が用意されています。

IDesignSpec GDI – GUIベースの次世代半導体仕様自動化ツール

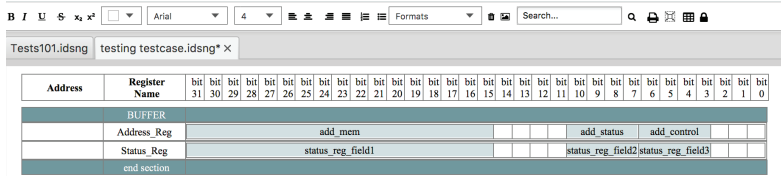

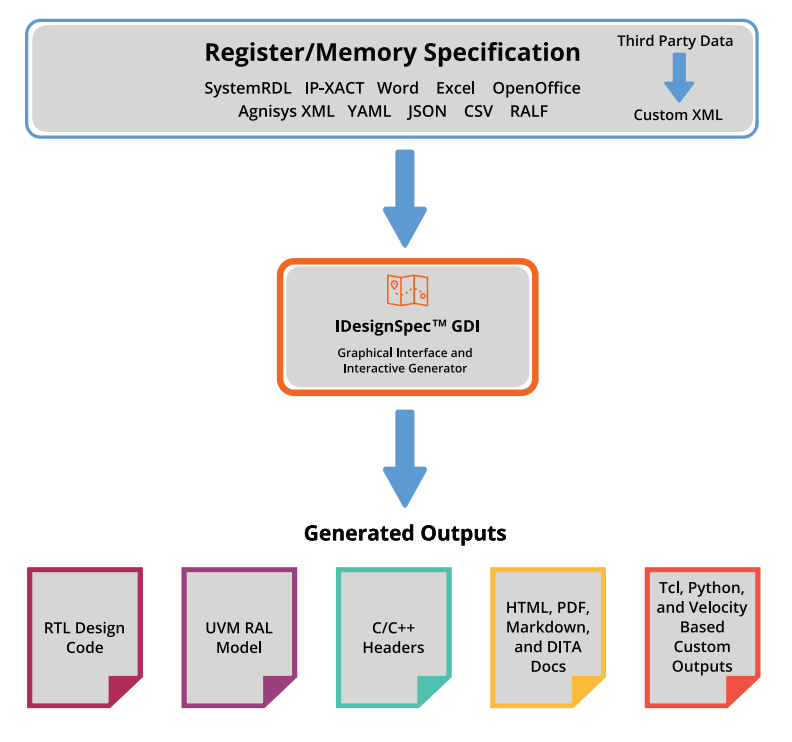

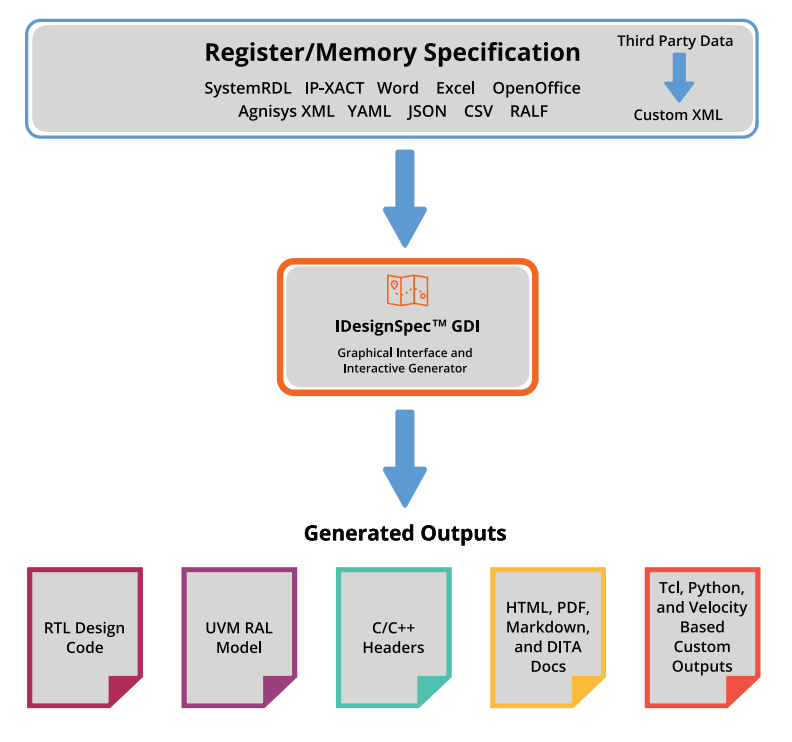

Agnisys社のIDesignSpec GDI(Graphical Design Interface)は、IPまたはSoCのメモリ、レジスタセット、レジスタフィールド向けに階層構造をモデリングし、各種ファイルを自動生成するための完全なソリューションを提供します。

SystemRDL、IP-XACT、JSON、RALF、YAML、XML、CSVファイルなどの、標準フォーマットで記述された既存データをIDesignSpec GDIインポートできます。

SoC開発のための強力なレジスタ/メモリエディタ&ジェネレータ

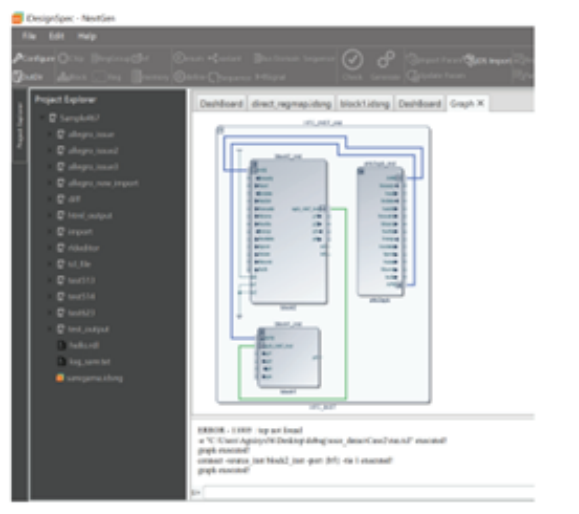

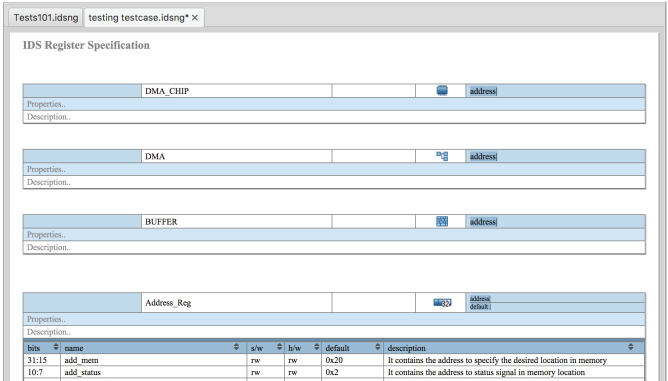

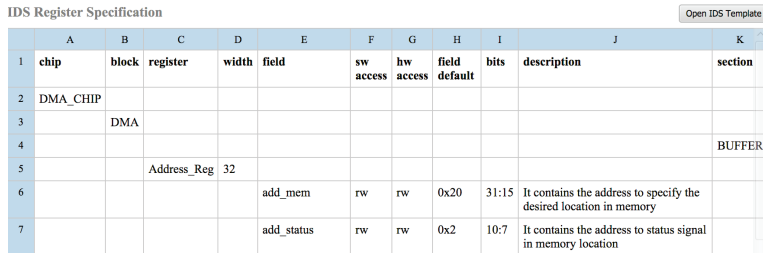

IDesignSpec GDIに付属されているIDS-NG、またはMicrosoft Word、Microsoft Excel、OpenOffice Calc向けアドオン機能を用いることで、Agnisysが提供するテンプレートを使用してレジスタとメモリを設定できます。最大の利点と柔軟性を得るために、IDS-NG に含まれる非常に直感的な特殊レジスタ、およびメモリエディタを選択することができます。IDS-NGは、プロジェクトに関連している各チーム向けに、さまざまなファイルやドキュメントを自動生成します。IDS-NGは、Gitリビジョン管理システムとの統合により、コラボレーションを促進しながら、テキスト・ファイルとグラフィック・データの両方を管理することで、SoCやIPの開発フローをシームレスにサポートします。

IDS-NGの特長

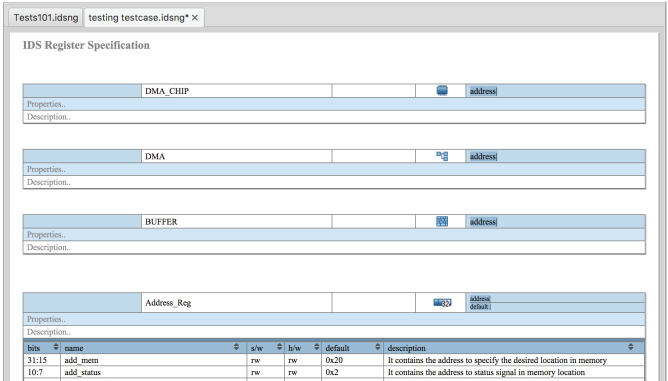

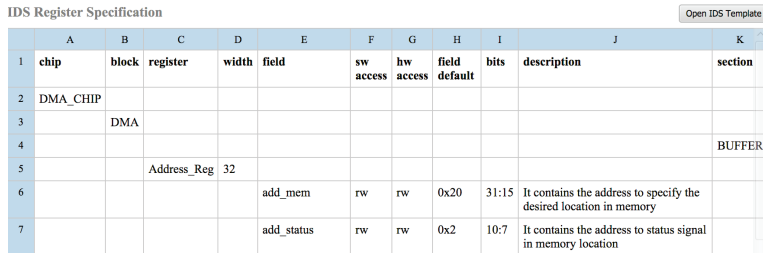

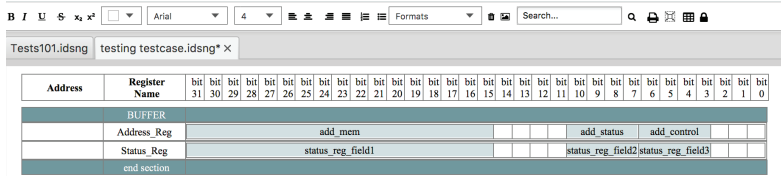

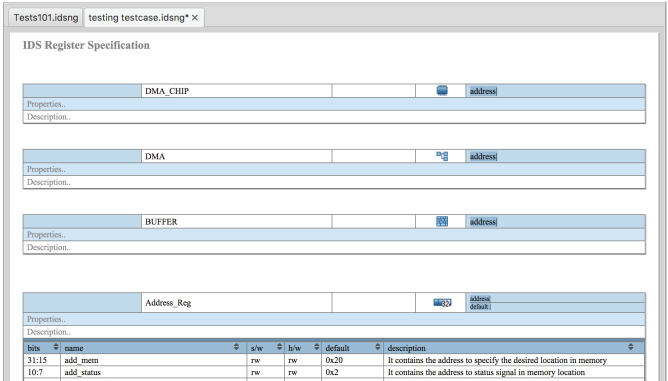

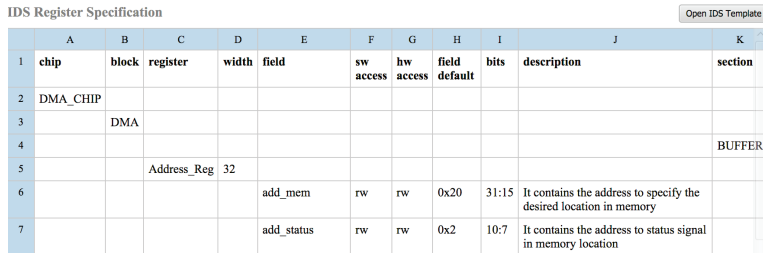

レジスタ情報は以下の各Viewで表示出来ます。

・Register View

・Spreadsheet View

・Param View

Viewを切り替えて、お好みの方法でデータの表示/編集ができます。

Register View

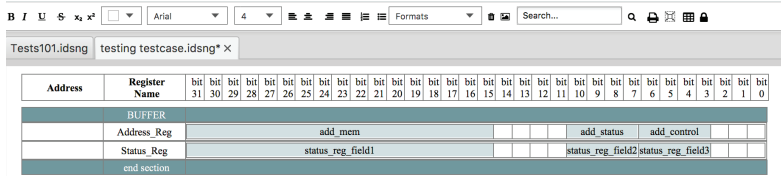

Spreadsheet View

Param View

Param View

Tcl、python、Velocityを用いることで、カスタマイズされた以下のファイルを出力できます。

・RTL(Verilog、SV)

・UVM Regモデル

・各種ヘッダファイル(Vヘッダ、SVヘッダ、vhdヘッダ、C/C++ヘッダ)

・JSON、YAML

・HTML、PDF、DITA

・SystemC

・IP-XACT、SystemRDL

・Markdown

IDesignSpec GDIの先進的な機能

・パラメータ化されたデザイン、さまざまなデザイン、低消費電力、複数のバス・ドメイン、パリティ/CRC/SECDED、クロック・ドメイン・クロッシング(CDC)、クロック・ゲーティングに対応

・AMBA 5、AHBLite、APB、AXI、AXILite、 AXI5、I2C、SPI、TileLink、Avalon、Wishbone用スレーブ・インタフェースに対応

・Velocityテンプレート、制約、カバレッジ仕様

・特殊レジスタ:: indirect, alias, ro/wo pair, interrupts, shadow, shared, locked, trigger buffered, counters, paged, FIFO, and virtualの各レジスタ対応

IDesignSpec GDIの特長

プロジェクトチームのためにこれら全てのファイルを自動生成することで、プロジェクトの初期段階での開発時間やリソースを節約できます。IDesignSpec GDIによってファイルは全て自動生成されますので、手作業でのコーディングが不要になります。また全てのファイルやドキュメントの自動生成によって、バグを排除し、設計と検証を大幅に加速します。

IDesignSpec GDIは、仕様が変更されるたびにさらなる価値を提供します。

仕様が変更されるたびに

・全ての関連ファイルを、簡単かつ自動的に再生成

・手動更新の手間を省き、すべてのチームが常に同期できます。

IDesignSpec GDIのその他の機能

・GITとの統合

・シーケンス・データだけでなく、レジスタ・データの差分と結合による同時編集

・複数プロジェクトをサポート

・プロジェクトベースの構成設定機能

・複数のOSをサポート- Linux、Windows、Mac

・SystemRDLエディタ

・Python/Tclエディタ

・Word/Excelのインポート

・AIによる自然言語(英語)から自動シーケンス生成

・標準ライブラリのブロックをインスタンス化

・SoC設計とアセンブリのためのIDS-Integrateとの統合

IDS-Batch CLI – コマンドライン・ベースの次世代半導体仕様自動化ツール

IDS-Batch CLI はコマンドライン・モードで実行され、プロジェクト内の各チームのために設計、検証、組み込みSW開発向け各種ファイルおよびドキュメントを自動生成します。

IDS-Batch CLI は、あらゆる SoC または IP 開発向けに活用可能です。

IDS-Batch CLIの特長

・レジスタ仕様書からWordその他形式のドキュメントを作成する機能

・出力されるドキュメントのフォーマットは、ユーザ定義のテンプレートで指定可能

・ファイル生成時に実データに置き換えられる特殊キーワードを理解する機能

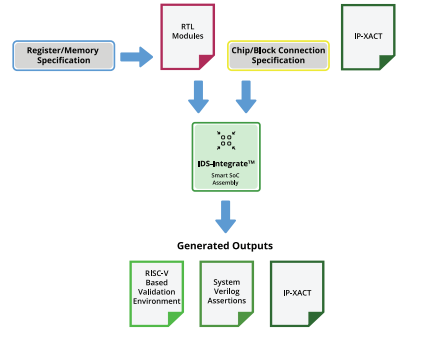

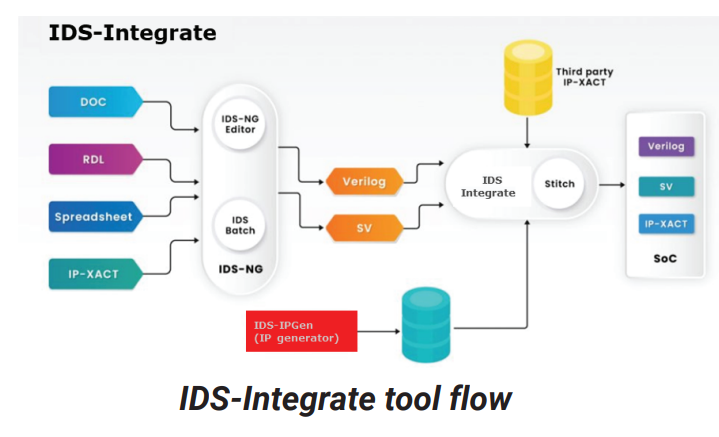

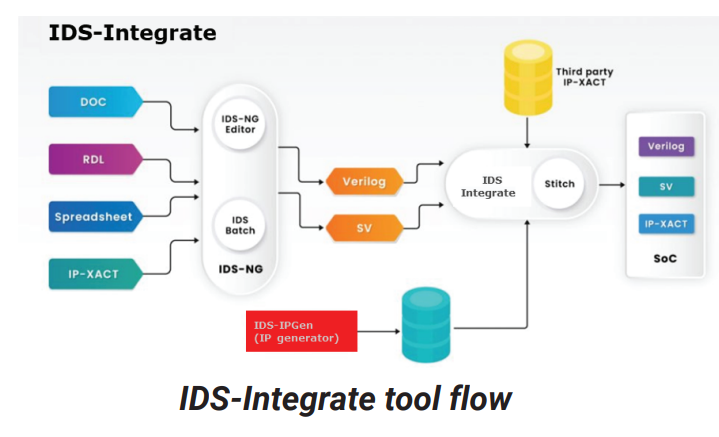

IDS-Integrate

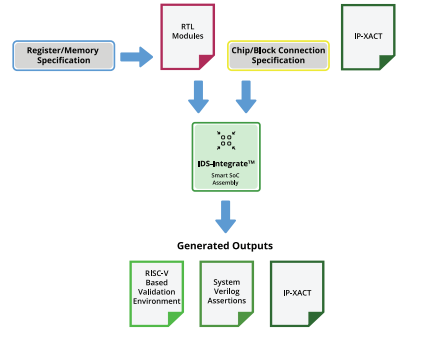

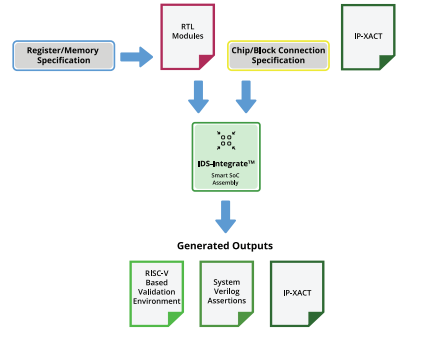

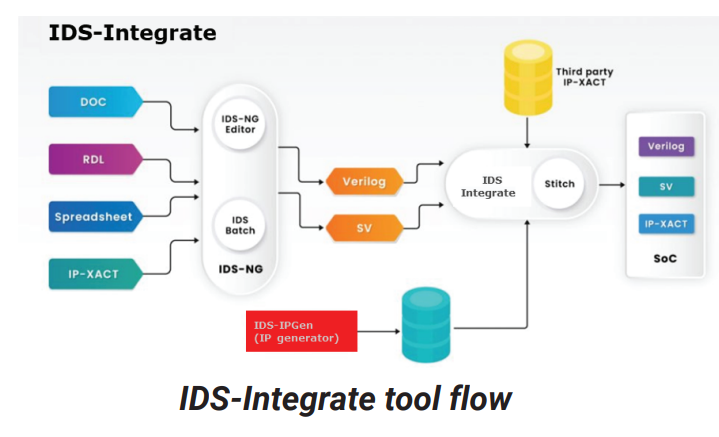

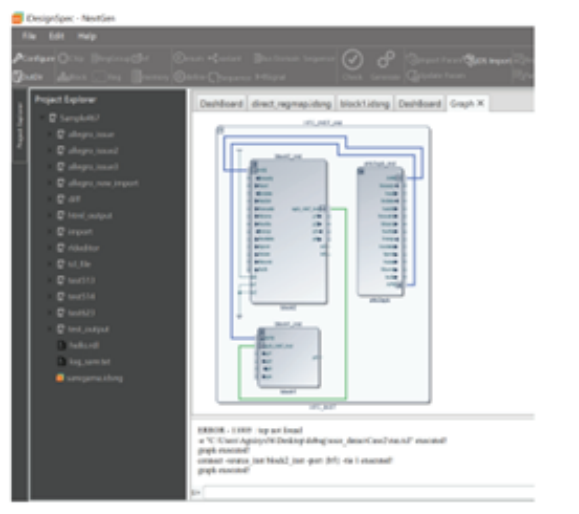

IDS-IntegrateはSoCアセンブリのために、お客様の設計要件を満たす柔軟でカスタマイズ可能な環境を提供します。

IDS-Integrateはブロックを相互接続するだけでなく、バス・マルチプレクサ、アグリゲータ、ブリッジ(AHB to APB、AXI to APB、AXI4-Full to AHB-Full)、などのRTLコードも生成します。またIDS-Integrateでは、IDesignSpecで生成されたレジスタ、RTLおよびIPブロックを完全に再利用できます。

一方でAgnisys が生成したデザインに限定されることはありません。IDS-Integrate では、IP-XACT 記述を持つあらゆるサードパーティの IP ブロックを扱うことができます。アプリケーション・ユーザはTclまたはPythonで、同一または類似した名前のブロック入出力ポート間のインテリジェント・ネーム・マッピングのルールなど、独自のブロックの相互接続方法を指定できます。IDS-Integrateは、これらの機能をもちいることで完全なトップレベルSoCを実装します。

入力データ

・IP-XACT

・RTL

・SystemRDL

・IDesignSpecのGDI仕様書(.docx、.xlsxなど)

出力データ

・Verilog / System Verilog RTL

・SystemVerilogアサーション

・各種フォーマットのドキュメント

・IP-XACT

・スケマティック・データ

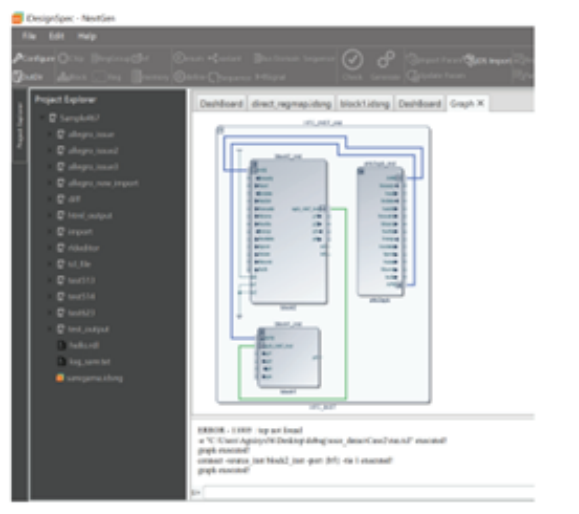

IDS-Integrateの特長

・繰り返しの作業を可能にする自動化されたプロセスを提供

・SoC開発のための時間を大幅に節約可能

・RTLブロックを相互接続する際の手作業によるコーディングミスを排除すると同時に、ユーザの仕様の確認を支援

・ブロックとその接続を直感的に理解できるグラフィカル表示

・チップ階層内のナビゲーションによる、ブロックとその接続の直感的なグラフィカル表示

IDS-Integrateの機能

・IP-XACTなどの標準規格(IEEE 1685-2014, 2009)に準拠、TGIをサポート

・TclおよびPython APIによるコマンドモード、およびIDesignSpecに完全に統合されたGUI(IDS-NG)モードをサポート

・IPの作成、パッケージング、統合、再利用およびSoC/FPGAのデザインを支援

・内蔵されているデザイン・ルール・チェッカによって、RTL生成前にデザインの接続性を検証

・ポートを抽象化して接続を効率的にキャプチャしたり、結線や意図的な未接続、その他の特殊なケースを必要に応じて指定したりできる柔軟性

Agnisys の主力ツールである IDesignSpec には、IDesignSpec GDI (グラフィカル版)と IDS-Batch CLI(コマンド版) の 2 種類が用意されています。

IDesignSpec GDI – GUIベースの次世代半導体仕様自動化ツール

Agnisys社のIDesignSpec GDI(Graphical Design Interface)は、IPまたはSoCのメモリ、レジスタセット、レジスタフィールド向けに階層構造をモデリングし、各種ファイルを自動生成するための完全なソリューションを提供します。

SystemRDL、IP-XACT、JSON、RALF、YAML、XML、CSVファイルなどの、標準フォーマットで記述された既存データをIDesignSpec GDIインポートできます。

SoC開発のための強力なレジスタ/メモリエディタ&ジェネレータ

IDesignSpec GDIに付属されているIDS-NG、またはMicrosoft Word、Microsoft Excel、OpenOffice Calc向けアドオン機能を用いることで、Agnisysが提供するテンプレートを使用してレジスタとメモリを設定できます。最大の利点と柔軟性を得るために、IDS-NG に含まれる非常に直感的な特殊レジスタ、およびメモリエディタを選択することができます。IDS-NGは、プロジェクトに関連している各チーム向けに、さまざまなファイルやドキュメントを自動生成します。IDS-NGは、Gitリビジョン管理システムとの統合により、コラボレーションを促進しながら、テキスト・ファイルとグラフィック・データの両方を管理することで、SoCやIPの開発フローをシームレスにサポートします。

IDS-NGの特長

レジスタ情報は以下の各Viewで表示出来ます。

・Register View

・Spreadsheet View

・Param View

Viewを切り替えて、お好みの方法でデータの表示/編集ができます。

Register View

Spreadsheet View

Param View

Param View

Tcl、python、Velocityを用いることで、カスタマイズされた以下のファイルを出力できます。

・RTL(Verilog、SV)

・UVM Regモデル

・各種ヘッダファイル(Vヘッダ、SVヘッダ、vhdヘッダ、C/C++ヘッダ)

・JSON、YAML

・HTML、PDF、DITA

・SystemC

・IP-XACT、SystemRDL

・Markdown

IDesignSpec GDIの先進的な機能

・パラメータ化されたデザイン、さまざまなデザイン、低消費電力、複数のバス・ドメイン、パリティ/CRC/SECDED、クロック・ドメイン・クロッシング(CDC)、クロック・ゲーティングに対応

・AMBA 5、AHBLite、APB、AXI、AXILite、 AXI5、I2C、SPI、TileLink、Avalon、Wishbone用スレーブ・インタフェースに対応

・Velocityテンプレート、制約、カバレッジ仕様

・特殊レジスタ:: indirect, alias, ro/wo pair, interrupts, shadow, shared, locked, trigger buffered, counters, paged, FIFO, and virtualの各レジスタ対応

IDesignSpec GDIの特長

プロジェクトチームのためにこれら全てのファイルを自動生成することで、プロジェクトの初期段階での開発時間やリソースを節約できます。IDesignSpec GDIによってファイルは全て自動生成されますので、手作業でのコーディングが不要になります。また全てのファイルやドキュメントの自動生成によって、バグを排除し、設計と検証を大幅に加速します。

IDesignSpec GDIは、仕様が変更されるたびにさらなる価値を提供します。

仕様が変更されるたびに

・全ての関連ファイルを、簡単かつ自動的に再生成

・手動更新の手間を省き、すべてのチームが常に同期できます。

IDesignSpec GDIのその他の機能

・GITとの統合

・シーケンス・データだけでなく、レジスタ・データの差分と結合による同時編集

・複数プロジェクトをサポート

・プロジェクトベースの構成設定機能

・複数のOSをサポート- Linux、Windows、Mac

・SystemRDLエディタ

・Python/Tclエディタ

・Word/Excelのインポート

・AIによる自然言語(英語)から自動シーケンス生成

・標準ライブラリのブロックをインスタンス化

・SoC設計とアセンブリのためのIDS-Integrateとの統合

IDS-Batch CLI – コマンドライン・ベースの次世代半導体仕様自動化ツール

IDS-Batch CLI はコマンドライン・モードで実行され、プロジェクト内の各チームのために設計、検証、組み込みSW開発向け各種ファイルおよびドキュメントを自動生成します。

IDS-Batch CLI は、あらゆる SoC または IP 開発向けに活用可能です。

IDS-Batch CLIの特長

・レジスタ仕様書からWordその他形式のドキュメントを作成する機能

・出力されるドキュメントのフォーマットは、ユーザ定義のテンプレートで指定可能

・ファイル生成時に実データに置き換えられる特殊キーワードを理解する機能

IDS-Integrate

IDS-IntegrateはSoCアセンブリのために、お客様の設計要件を満たす柔軟でカスタマイズ可能な環境を提供します。

IDS-Integrateはブロックを相互接続するだけでなく、バス・マルチプレクサ、アグリゲータ、ブリッジ(AHB to APB、AXI to APB、AXI4-Full to AHB-Full)、などのRTLコードも生成します。またIDS-Integrateでは、IDesignSpecで生成されたレジスタ、RTLおよびIPブロックを完全に再利用できます。

一方でAgnisys が生成したデザインに限定されることはありません。IDS-Integrate では、IP-XACT 記述を持つあらゆるサードパーティの IP ブロックを扱うことができます。アプリケーション・ユーザはTclまたはPythonで、同一または類似した名前のブロック入出力ポート間のインテリジェント・ネーム・マッピングのルールなど、独自のブロックの相互接続方法を指定できます。IDS-Integrateは、これらの機能をもちいることで完全なトップレベルSoCを実装します。

入力データ

・IP-XACT

・RTL

・SystemRDL

・IDesignSpecのGDI仕様書(.docx、.xlsxなど)

出力データ

・Verilog / System Verilog RTL

・SystemVerilogアサーション

・各種フォーマットのドキュメント

・IP-XACT

・スケマティック・データ

IDS-Integrateの特長

・繰り返しの作業を可能にする自動化されたプロセスを提供

・SoC開発のための時間を大幅に節約可能

・RTLブロックを相互接続する際の手作業によるコーディングミスを排除すると同時に、ユーザの仕様の確認を支援

・ブロックとその接続を直感的に理解できるグラフィカル表示

・チップ階層内のナビゲーションによる、ブロックとその接続の直感的なグラフィカル表示

IDS-Integrateの機能

・IP-XACTなどの標準規格(IEEE 1685-2014, 2009)に準拠、TGIをサポート

・TclおよびPython APIによるコマンドモード、およびIDesignSpecに完全に統合されたGUI(IDS-NG)モードをサポート

・IPの作成、パッケージング、統合、再利用およびSoC/FPGAのデザインを支援

・内蔵されているデザイン・ルール・チェッカによって、RTL生成前にデザインの接続性を検証

・ポートを抽象化して接続を効率的にキャプチャしたり、結線や意図的な未接続、その他の特殊なケースを必要に応じて指定したりできる柔軟性

Agnisys の主力ツールである IDesignSpec には、IDesignSpec GDI (グラフィカル版)と IDS-Batch CLI(コマンド版) の 2 種類が用意されています。

IDesignSpec GDI – GUIベースの次世代半導体仕様自動化ツール

Agnisys社のIDesignSpec GDI(Graphical Design Interface)は、IPまたはSoCのメモリ、レジスタセット、レジスタフィールド向けに階層構造をモデリングし、各種ファイルを自動生成するための完全なソリューションを提供します。

SystemRDL、IP-XACT、JSON、RALF、YAML、XML、CSVファイルなどの、標準フォーマットで記述された既存データをIDesignSpec GDIインポートできます。

SoC開発のための強力なレジスタ/メモリエディタ&ジェネレータ

IDesignSpec GDIに付属されているIDS-NG、またはMicrosoft Word、Microsoft Excel、OpenOffice Calc向けアドオン機能を用いることで、Agnisysが提供するテンプレートを使用してレジスタとメモリを設定できます。最大の利点と柔軟性を得るために、IDS-NG に含まれる非常に直感的な特殊レジスタ、およびメモリエディタを選択することができます。IDS-NGは、プロジェクトに関連している各チーム向けに、さまざまなファイルやドキュメントを自動生成します。IDS-NGは、Gitリビジョン管理システムとの統合により、コラボレーションを促進しながら、テキスト・ファイルとグラフィック・データの両方を管理することで、SoCやIPの開発フローをシームレスにサポートします。

IDS-NGの特長

レジスタ情報は以下の各Viewで表示出来ます。

・Register View

・Spreadsheet View

・Param View

Viewを切り替えて、お好みの方法でデータの表示/編集ができます。

Register View

Spreadsheet View

Param View

Param View

Tcl、python、Velocityを用いることで、カスタマイズされた以下のファイルを出力できます。

・RTL(Verilog、SV)

・UVM Regモデル

・各種ヘッダファイル(Vヘッダ、SVヘッダ、vhdヘッダ、C/C++ヘッダ)

・JSON、YAML

・HTML、PDF、DITA

・SystemC

・IP-XACT、SystemRDL

・Markdown

IDesignSpec GDIの先進的な機能

・パラメータ化されたデザイン、さまざまなデザイン、低消費電力、複数のバス・ドメイン、パリティ/CRC/SECDED、クロック・ドメイン・クロッシング(CDC)、クロック・ゲーティングに対応

・AMBA 5、AHBLite、APB、AXI、AXILite、 AXI5、I2C、SPI、TileLink、Avalon、Wishbone用スレーブ・インタフェースに対応

・Velocityテンプレート、制約、カバレッジ仕様

・特殊レジスタ:: indirect, alias, ro/wo pair, interrupts, shadow, shared, locked, trigger buffered, counters, paged, FIFO, and virtualの各レジスタ対応

IDesignSpec GDIの特長

プロジェクトチームのためにこれら全てのファイルを自動生成することで、プロジェクトの初期段階での開発時間やリソースを節約できます。IDesignSpec GDIによってファイルは全て自動生成されますので、手作業でのコーディングが不要になります。また全てのファイルやドキュメントの自動生成によって、バグを排除し、設計と検証を大幅に加速します。

IDesignSpec GDIは、仕様が変更されるたびにさらなる価値を提供します。

仕様が変更されるたびに

・全ての関連ファイルを、簡単かつ自動的に再生成

・手動更新の手間を省き、すべてのチームが常に同期できます。

IDesignSpec GDIのその他の機能

・GITとの統合

・シーケンス・データだけでなく、レジスタ・データの差分と結合による同時編集

・複数プロジェクトをサポート

・プロジェクトベースの構成設定機能

・複数のOSをサポート- Linux、Windows、Mac

・SystemRDLエディタ

・Python/Tclエディタ

・Word/Excelのインポート

・AIによる自然言語(英語)から自動シーケンス生成

・標準ライブラリのブロックをインスタンス化

・SoC設計とアセンブリのためのIDS-Integrateとの統合

IDS-Batch CLI – コマンドライン・ベースの次世代半導体仕様自動化ツール

IDS-Batch CLI はコマンドライン・モードで実行され、プロジェクト内の各チームのために設計、検証、組み込みSW開発向け各種ファイルおよびドキュメントを自動生成します。

IDS-Batch CLI は、あらゆる SoC または IP 開発向けに活用可能です。

IDS-Batch CLIの特長

・レジスタ仕様書からWordその他形式のドキュメントを作成する機能

・出力されるドキュメントのフォーマットは、ユーザ定義のテンプレートで指定可能

・ファイル生成時に実データに置き換えられる特殊キーワードを理解する機能

IDS-Integrate

IDS-IntegrateはSoCアセンブリのために、お客様の設計要件を満たす柔軟でカスタマイズ可能な環境を提供します。

IDS-Integrateはブロックを相互接続するだけでなく、バス・マルチプレクサ、アグリゲータ、ブリッジ(AHB to APB、AXI to APB、AXI4-Full to AHB-Full)、などのRTLコードも生成します。またIDS-Integrateでは、IDesignSpecで生成されたレジスタ、RTLおよびIPブロックを完全に再利用できます。

一方でAgnisys が生成したデザインに限定されることはありません。IDS-Integrate では、IP-XACT 記述を持つあらゆるサードパーティの IP ブロックを扱うことができます。アプリケーション・ユーザはTclまたはPythonで、同一または類似した名前のブロック入出力ポート間のインテリジェント・ネーム・マッピングのルールなど、独自のブロックの相互接続方法を指定できます。IDS-Integrateは、これらの機能をもちいることで完全なトップレベルSoCを実装します。

入力データ

・IP-XACT

・RTL

・SystemRDL

・IDesignSpecのGDI仕様書(.docx、.xlsxなど)

出力データ

・Verilog / System Verilog RTL

・SystemVerilogアサーション

・各種フォーマットのドキュメント

・IP-XACT

・スケマティック・データ

IDS-Integrateの特長

・繰り返しの作業を可能にする自動化されたプロセスを提供

・SoC開発のための時間を大幅に節約可能

・RTLブロックを相互接続する際の手作業によるコーディングミスを排除すると同時に、ユーザの仕様の確認を支援

・ブロックとその接続を直感的に理解できるグラフィカル表示

・チップ階層内のナビゲーションによる、ブロックとその接続の直感的なグラフィカル表示

IDS-Integrateの機能

・IP-XACTなどの標準規格(IEEE 1685-2014, 2009)に準拠、TGIをサポート

・TclおよびPython APIによるコマンドモード、およびIDesignSpecに完全に統合されたGUI(IDS-NG)モードをサポート

・IPの作成、パッケージング、統合、再利用およびSoC/FPGAのデザインを支援

・内蔵されているデザイン・ルール・チェッカによって、RTL生成前にデザインの接続性を検証

・ポートを抽象化して接続を効率的にキャプチャしたり、結線や意図的な未接続、その他の特殊なケースを必要に応じて指定したりできる柔軟性